# High-Speed Hardware Interface Development With Design of Experiments Richard Allred & Barry Katz, SiSoft

#### Abstract

- The explosive growth of internet usage brings with it a huge demand in bandwidth capabilities. This has forced the computer communication industry to continually push the limits to improve line speed, density and power consumption of communication links.

- The design of these links is a highly complex task, where multiple objectives such as cost, performance and power must be weighed to create a competitive product. This poster describes and demonstrates how the Design of Experiments and Response Surface Modeling techniques were used to answer design problems, to quantify manufacturing variation and estimate Yield performance. This effort resulted in the industry's first 100 Gigabit Ethernet CMOS PHY chipset.

#### Objective

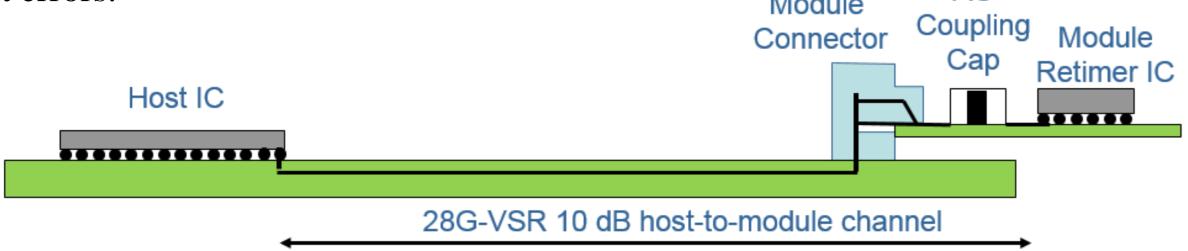

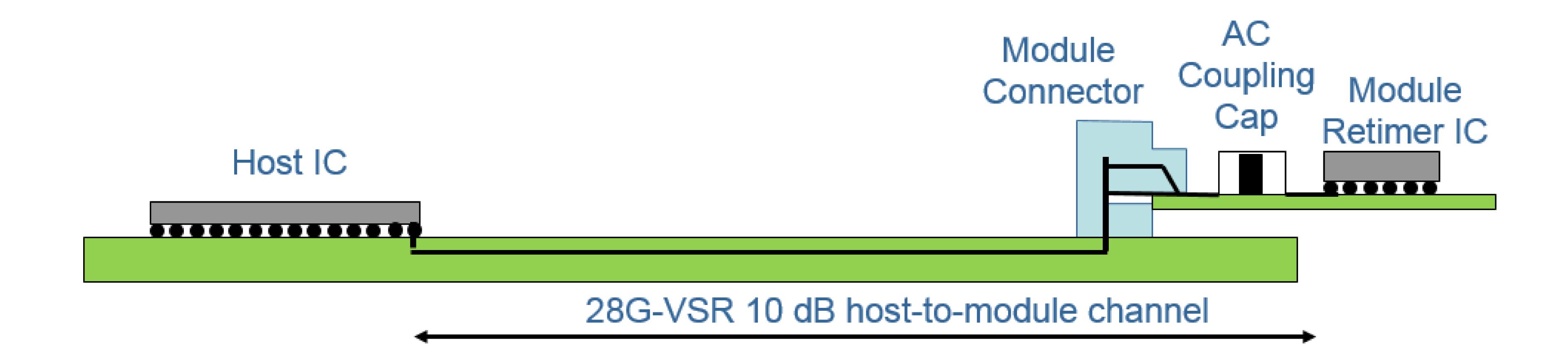

• Design a high speed 28G-VSR computer interface or link with a low probability of bit errors.

Module

AC

- A data rate of 28 Giga-bits per second (Gbps) means that the receiver of the link has only ~35 ps to decide if a 1 or 0 was sent.

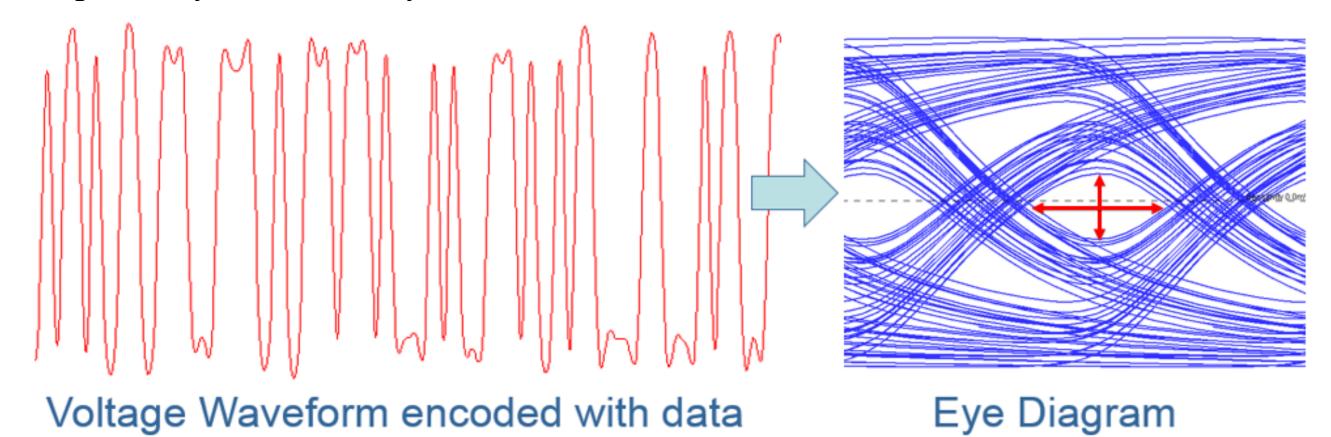

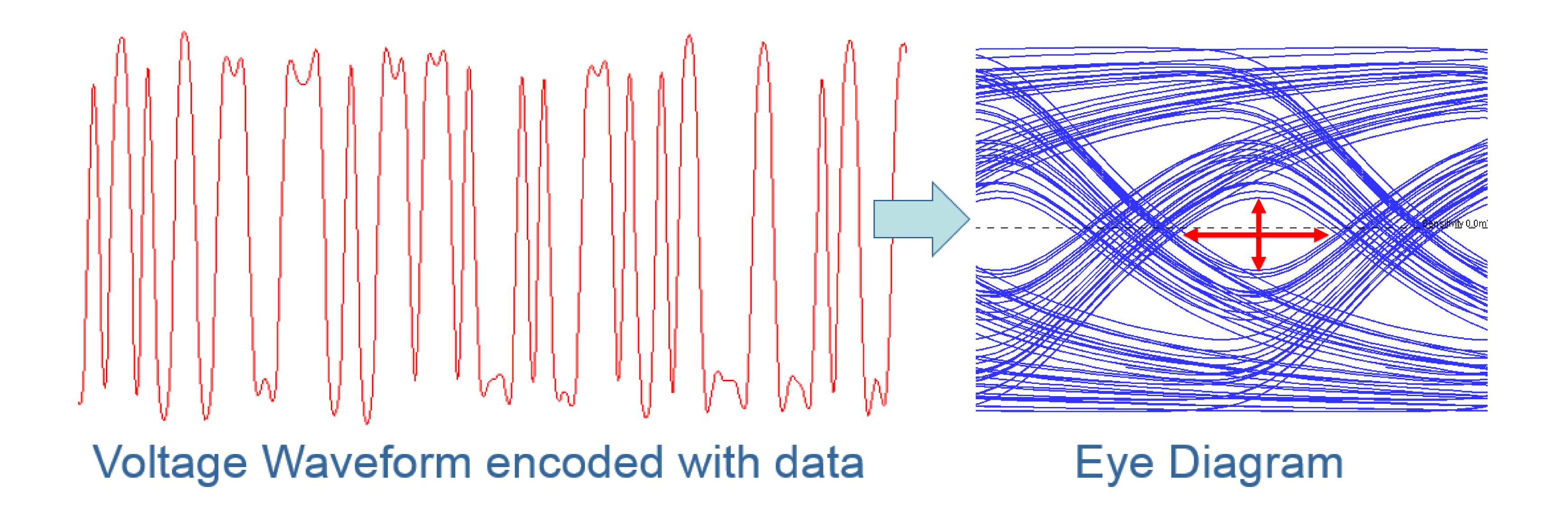

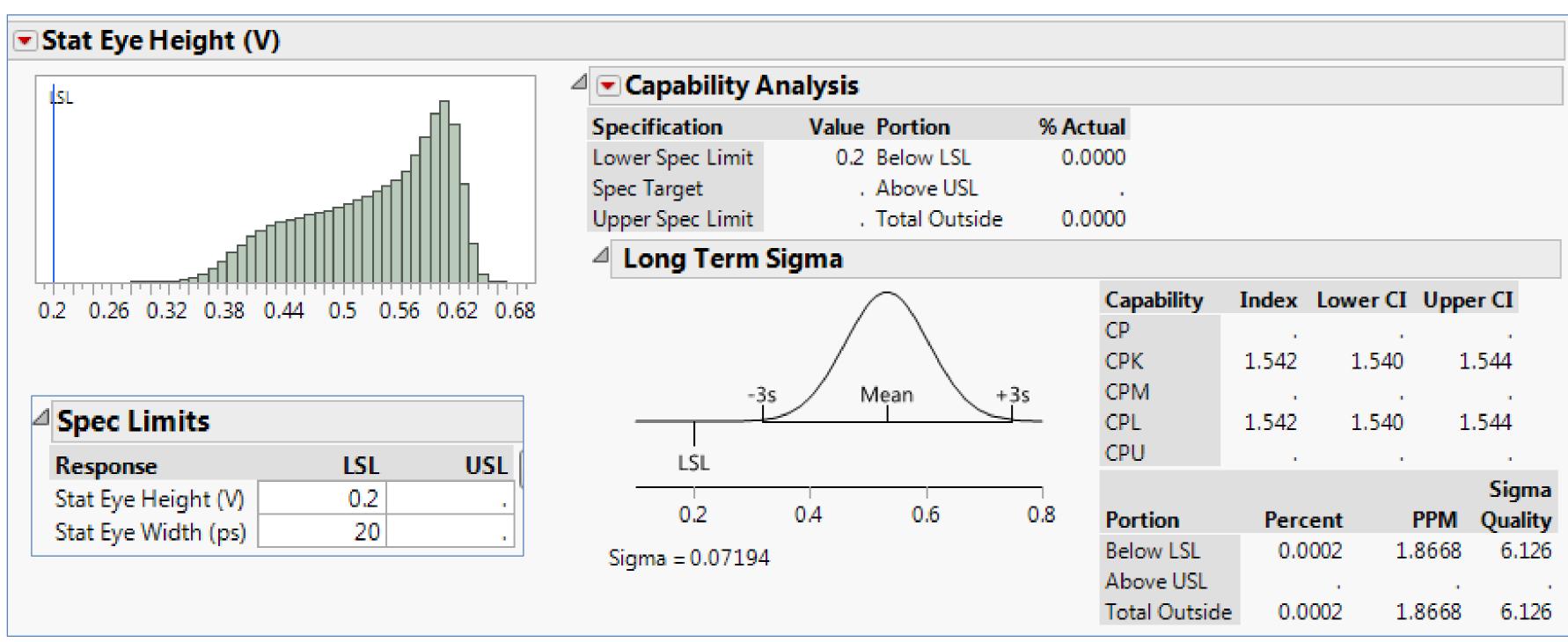

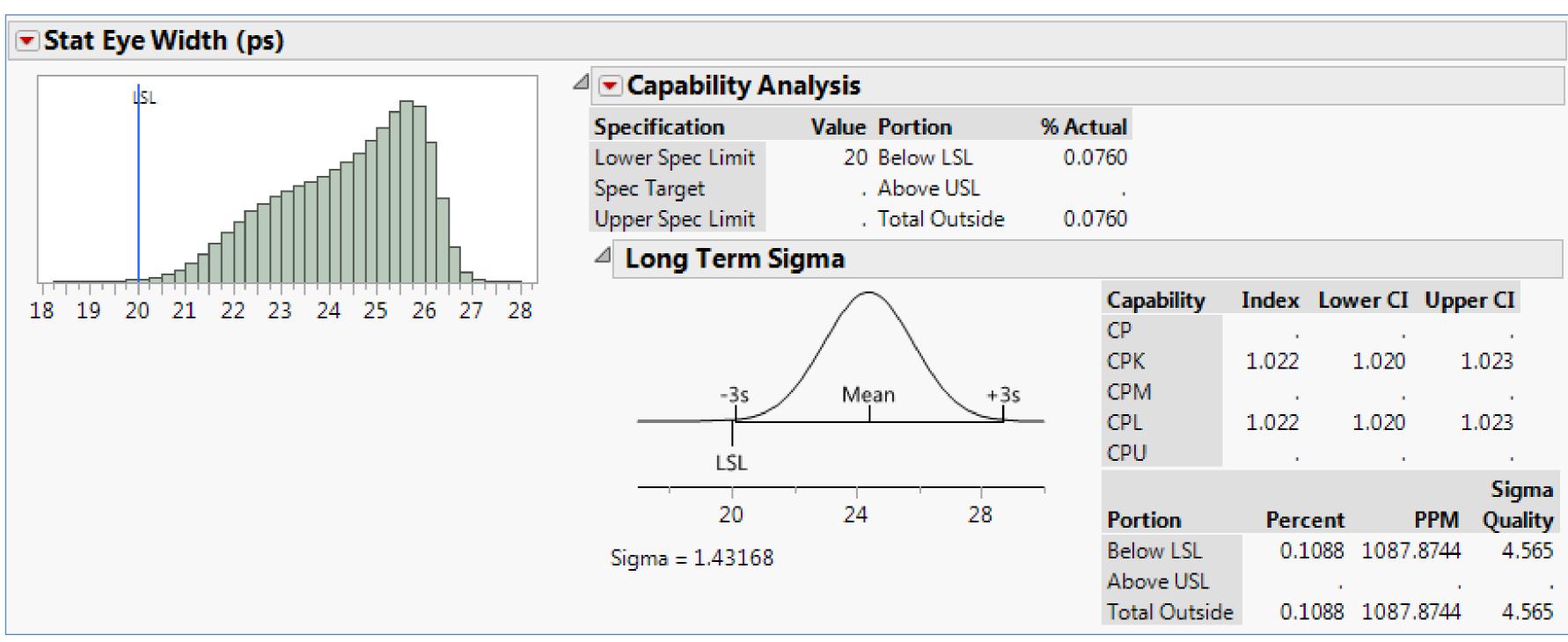

- •One measure of the goodness of a link is the voltage eye diagram inner height and width. The lower spec limit for eye height and width is 200 mV and 20 ps respectively. Additionally a PPM limit of 1000 is desired.

#### Method

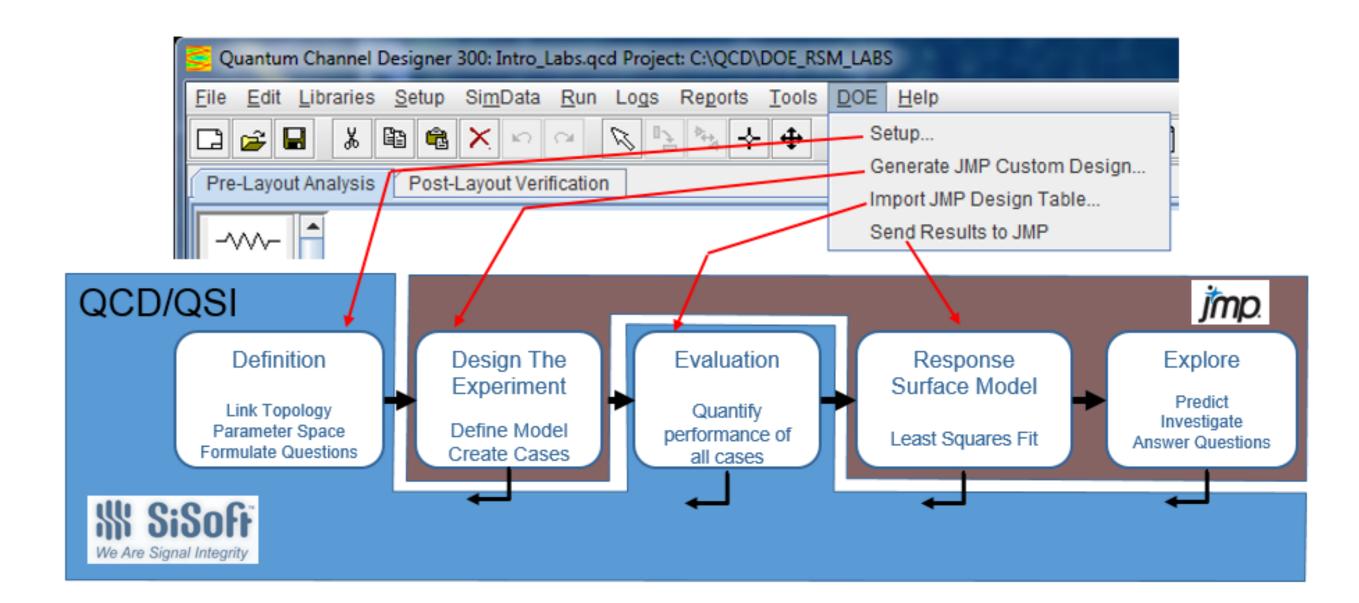

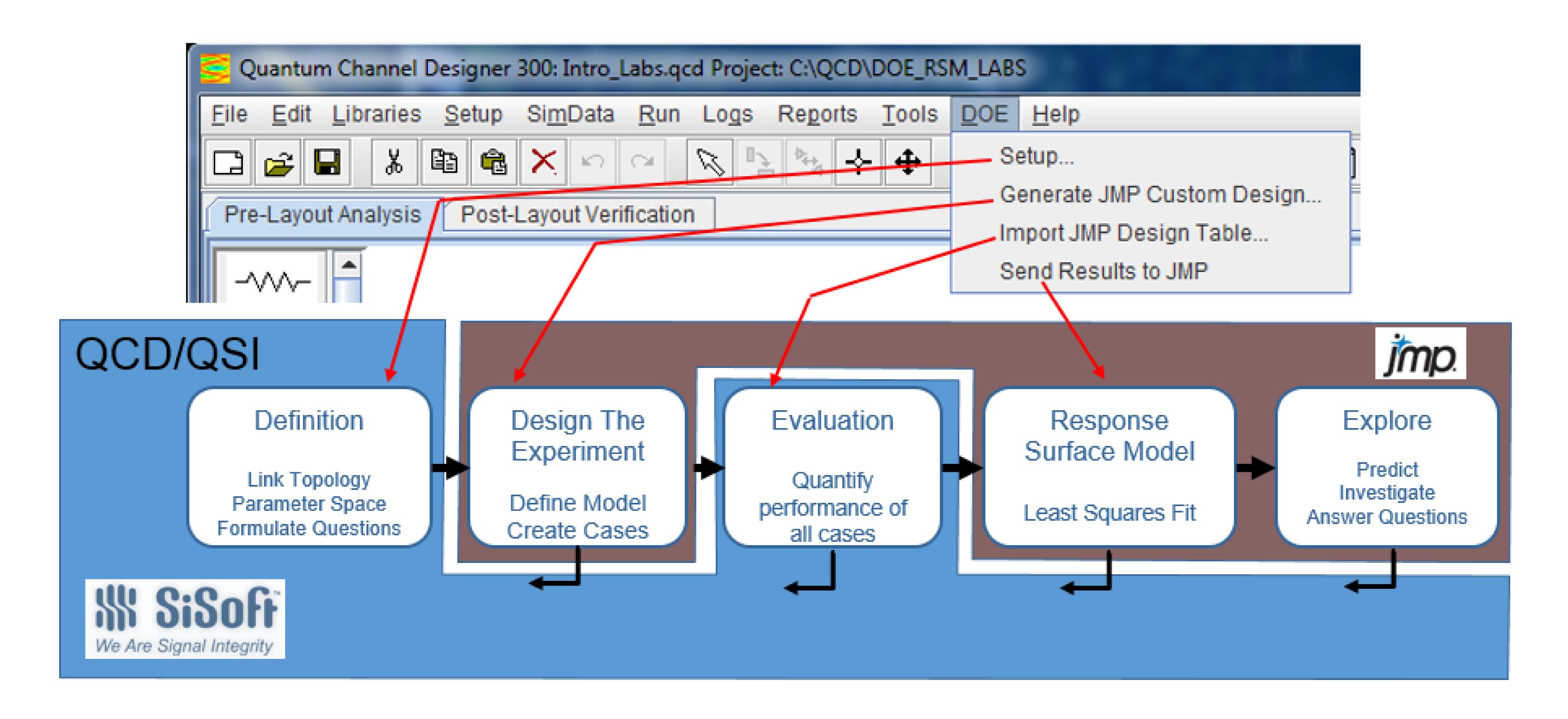

- We utilized SiSoft's advanced computer interface simulation techniques to virtually construct and test many different configurations.

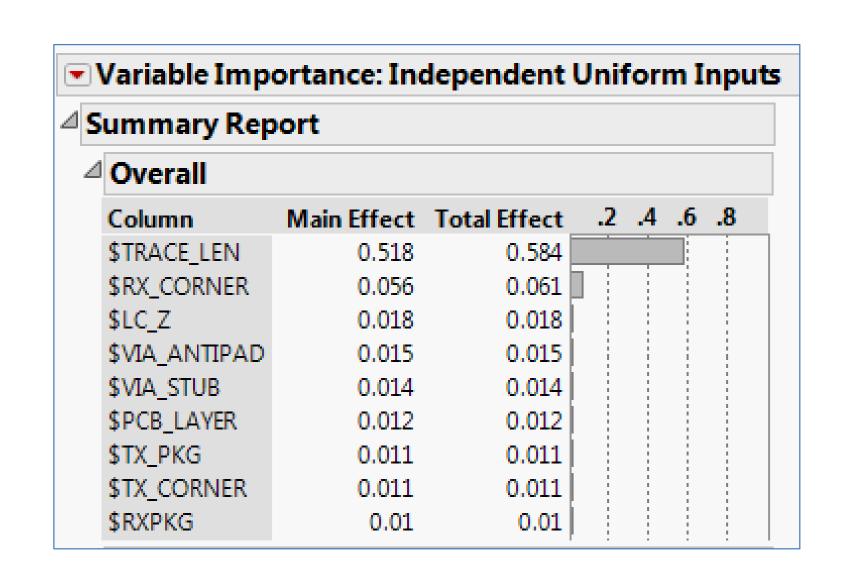

- Utilizing past experience, 9 factors were selected to explore the space: 3 design factors and 6 manufacturing factors (uncontrolled). Factor Details.

- Most of the factors are discrete and a full factorial design required 26,244 simulations which would take **58 hours** of compute time.

- A D-Optimal RSM model with 171 runs (3 times the minimum) were used to sample the factor space. This required only **20 minutes** of compute time.

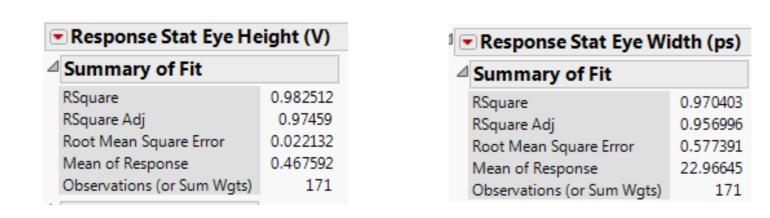

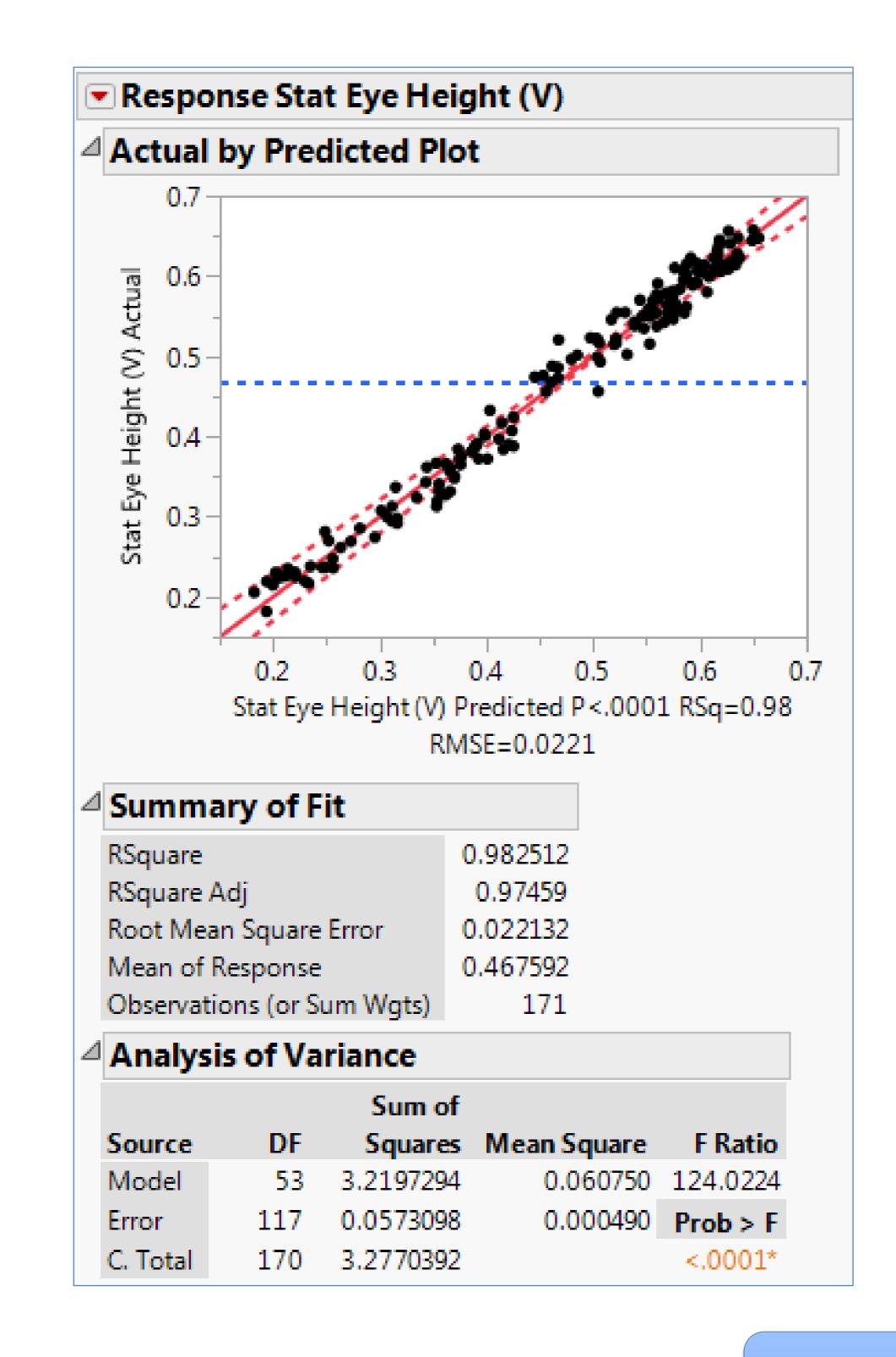

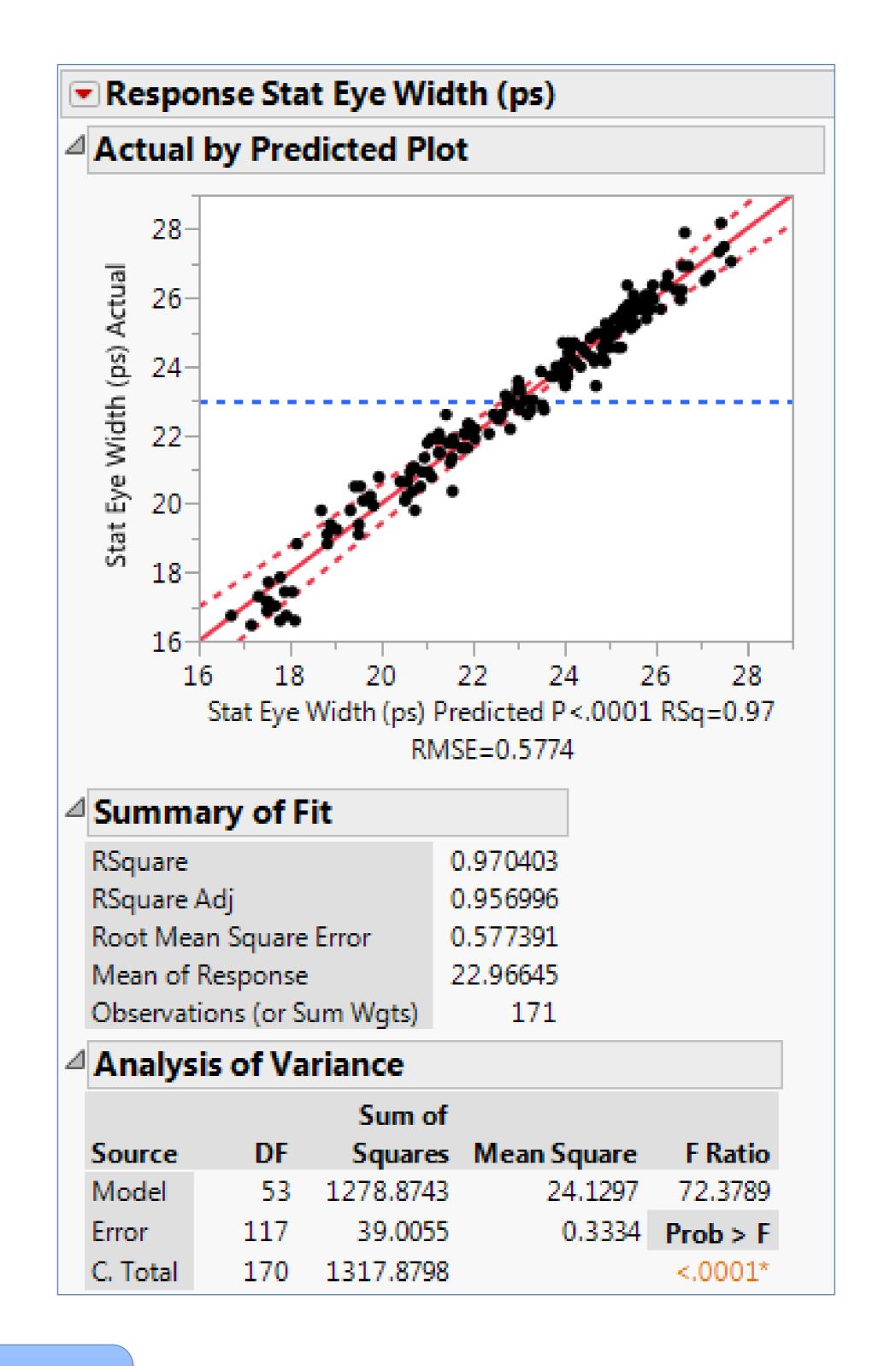

- A RSM model was used which yielded excellent fits on the eye height and width.

#### Results

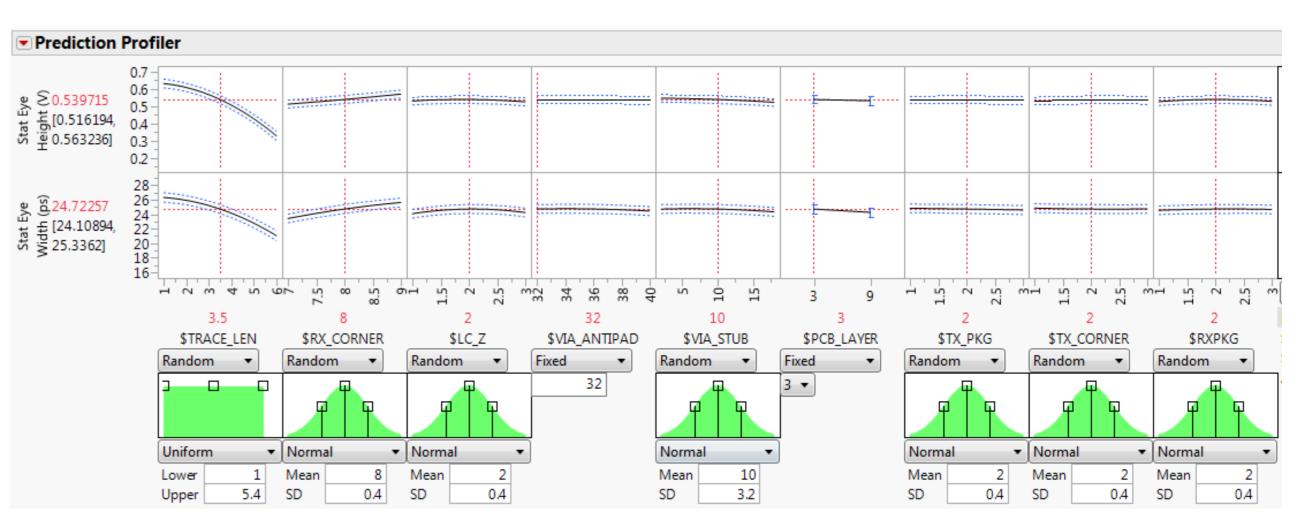

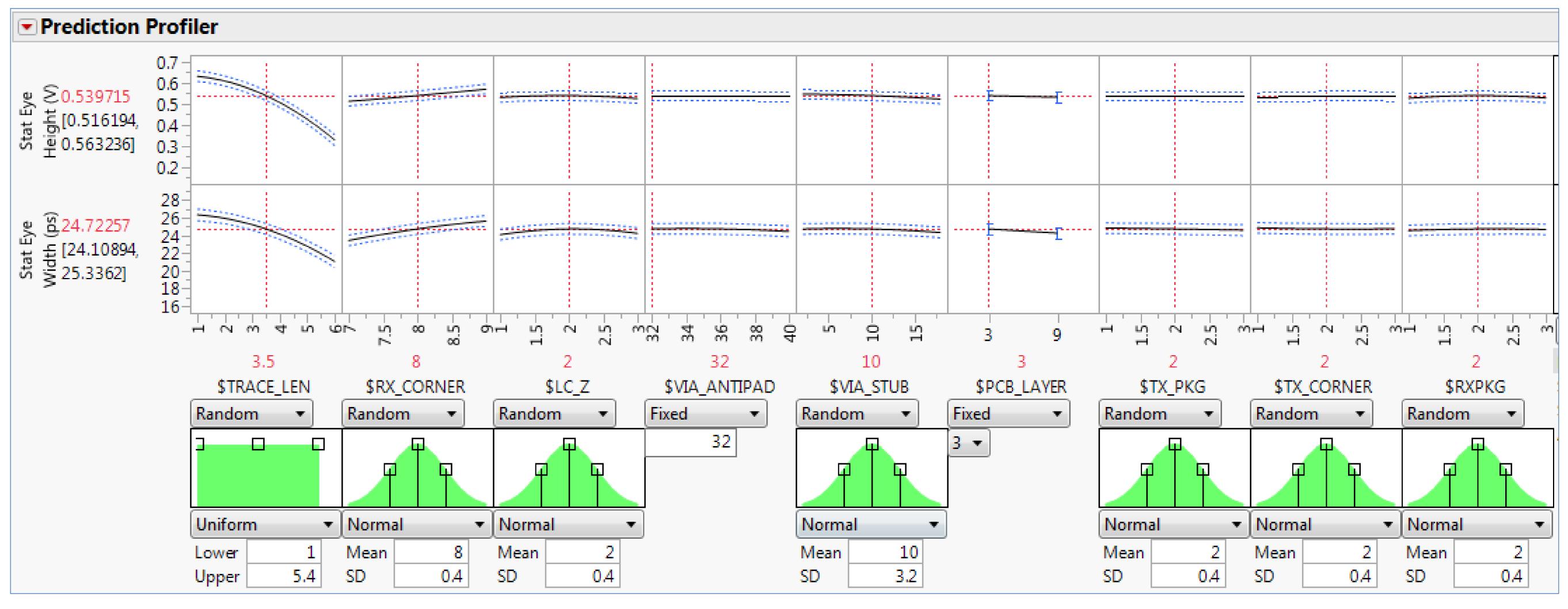

- The Prediction Profiler was used to predict the worst case operating conditions. Two of the design factors (printed circuit board (PCB) layer and via anti-pad size) were used to improve the worst case performance.

- The Simulator was utilized to assign distributions to the manufacturing factors and to quantify the probability of the worst case condition occurring through PPM analysis.

- The upper limit of the PCB trace length, the most signification of the factors and the last design factor, was reduced to 5.4 inches which yielded a PPM of around 1087.

#### Conclusions

- It has been demonstrated that the design of a challenging state of the art computer system can be greatly enhance by utilizing Design of Experiments and response surface modeling. Alternative methods of design space exploration require many more manual decisions which can often lead to sub-optimal results.

- Utilizing this methodology, the round trip analysis from the design of the experiment to the analysis typically takes only minutes. This allows for the designer to quickly iterate designs to balance trade-offs and inform design decisions. SiSoft has worked closely with JMP to integrate the tools to allows for this analysis.

About the Authors

## 28G VSR Channel Diagram

# Eye Diagram

### Factor Details

| Parameter Name                     | Factor Type   | Min    | Тур     | Max     |

|------------------------------------|---------------|--------|---------|---------|

| Tx PVT Corner                      | Manufacturing | SS     | TT      | FF      |

| Tx PKG                             | Manufacturing | 90 Ohm | 100 Ohm | 110 Ohm |

| Line Card PCB<br>Via Anti-Pad Size | Design        | 32 mil | 36 mil  | 40 mil  |

| Line Card PCB<br>Via Stub length   | Manufacturing | 2 mil  | 10 mil  | 18 mil  |

| Line Card PCB<br>Routing Layer     | Design        | 3      |         | 9       |

| Line Card length                   | Design        | 1 inch | 3 inch  | 6 inch  |

| Line Card TL<br>Impedance          | Manufacturing | 90 Ohm | 100 Ohm | 110 Ohm |

| Rx PKG                             | Manufacturing | 90 Ohm | 100 Ohm | 110 Ohm |

| Rx PVT Corner                      | Manufacturing | SS     | TT      | FF      |

Table 1: 28G VSR interface factor space definition.

HOME

- •Full factorial design requires 26,244 simulations which would take **58 hours** of compute time.

- •A D-Optimal RSM model with 171 runs (3 times the minimum) were used to sample the factor space. This required only **20 minutes** of compute time.

### JMP/SiSoft Analysis Flow

### Model Fit Summary

### Analysis Details

#### About the Authors

- Richard Allred is a Senior Member of Technical Staff at SiSoft where he is responsible for the modeling the industry's cutting edge transmitter and receivers and well as contributes to tool and analysis development. Previously, Richard worked at Inphi and Intel where he designed serial and parallel computer interfaces for high end applications. Richard received his MSEE from University of Utah, and has 5 publications.

- Barry Katz, President and CTO for SiSoft, founded SiSoft in 1995. As CTO, Barry is responsible for leading the definition and development of SiSoft's products. He has devoted much of his efforts at SiSoft to delivering a comprehensive design methodology, software tools, and expert consulting to solve the problems faced by designers of leading edge high-speed systems. He was the founding chairman of the IBIS Quality committee. Barry received an MSEE degree from Carnegie Mellon and a BSEE degree from the University of Florida.

www.sisoft.com

### References

- Hall, S. & Heck H. (2009). Advanced Signal Integrity for High-Speed Digital Designs.

- Goos, P. & Jones, B. (2011). Optimal Design of Experiments: A Case Study Approach.